# High Power Density 650V Half-Bridge

# **GaN Transistors with Gate Driver**

### **General description**

The CGC02002 is an advanced system-inpackage (SIP) power ICs, consisting of gate driver and two 650-V enhancement-mode GaN power transistors in half-bridge configuration.

The integrated GaN power transistors have  $R_{DS(on)}$  of 190 m $\Omega$  and 190 m $\Omega$  for high- and low-side and drain-source blocking voltage of 650 V.

The CGC02002 features wide power supply range. And the high-side driver can be easily supplied by bootstrap circuit. Both the high-side and low-side gate drive voltage (VDDH and VDDL) is provided by internal voltage regulator, making an easy circuit design.

The CGC02002 features UVLO function for both high-side and low-side driving sections, preventing GaN transistors from operating in low-efficiency or unsafe conditions. The programmable deadtime function can avoid cross-conduction conditions.

The input signal pin arrangement allows easy interfacing with controllers.

The CGC02002 operates in the industrial temperature range of -40 °C to 125 °C. The device is in available in 9mm\*9mm QFN package.

### **Features**

- Integrated half-bridge GaN transistors with gate driver

- 650V drain-source blocking capabilities

- High/low-side  $R_{DS(on)}$  of 140/190 m $\Omega$

- Zero reverse recovery loss

- Ultra-low standby current

- Wide power supply range (10V~18V)

- Programmable deadtime (20ns~100ns)

- UVLO protections for high-side and low-side

- Over-temperature protection (OTP)

- QFN 9\*9 package

- Operating temperature of -40 °C to 125 °C

- Bill of material (BOM) reduction

- Very compact and simplified layout

- Flexible and easy design

## **Typical applications**

- Switch-mode power supplies

- Chargers and adaptors

- DC/DC, DC/AC converters

- ACF, AHB, LLC, totem-pole PFC

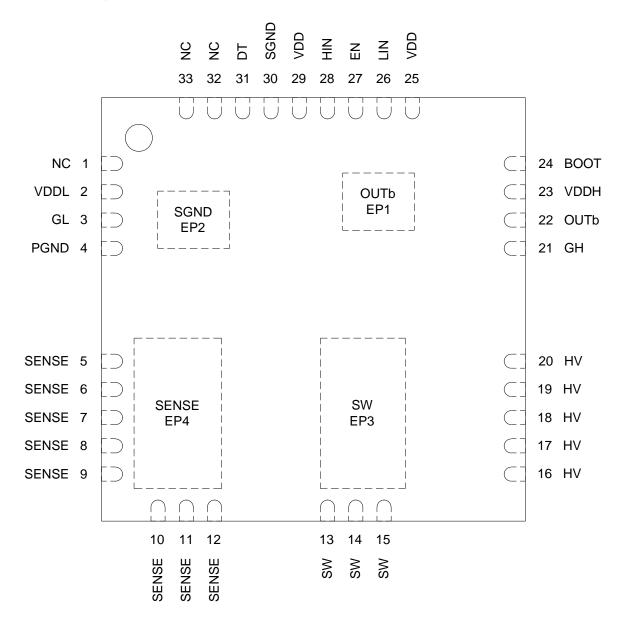

## Pin configuration and functions

## **Pin list**

| Pin #                   | Name  | I/O | Description                                                                                                             |

|-------------------------|-------|-----|-------------------------------------------------------------------------------------------------------------------------|

| 2                       | VDDL  | Ρ   | Gate driver low-side supply voltage. A ceramic capacitor of not less than 100nF must be connected between VDDL and PGND |

| 3                       | GL    | 0   | Low-side GaN gate                                                                                                       |

| 4                       | PGND  | G   | Gate driver low-side drive reference, internally connected to SENSE                                                     |

| 5,6,7,8,9,10,11,12, EP4 | SENSE | Р   | Half-bridge sense (low-side GaN source)                                                                                 |

| 13,14,15, EP3           | SW    | 0   | Half-bridge output                                                                                                      |

### CGC02002 DATASHEET 650V Half-Bridge GaN Transistors with Gate Driver

| 16,17,18,19,20 | HV   | Р  | High-voltage power supply (High side GaN drain)                                                                          |  |  |  |  |  |

|----------------|------|----|--------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| 21             | GH   | 0  | High-side GaN gate                                                                                                       |  |  |  |  |  |

| 22, EP1        | OUTb | G  | Gate driver high-side reference voltage, used only for<br>bootstrap capacitor connection, internally connected<br>to SW  |  |  |  |  |  |

| 23             | VDDH | Ρ  | Gate driver high-side supply voltage. A ceramic capacitor of not less than 100nF must be connected between VDDH and OUTb |  |  |  |  |  |

| 24             | BOOT | Р  | Power supply for high-side regulator (bootstrap voltage)                                                                 |  |  |  |  |  |

| 25,29          | VDD  | Р  | Power supply for logic and low-side regulator                                                                            |  |  |  |  |  |

| 26             | LIN  | I  | Low-side driver logic input                                                                                              |  |  |  |  |  |

| 27             | EN   | I  | Dual drivers enabling logic input                                                                                        |  |  |  |  |  |

| 28             | HIN  | I  | High-side driver logic input                                                                                             |  |  |  |  |  |

| 30, EP2        | SGND | G  | Logic ground                                                                                                             |  |  |  |  |  |

| 31             | DT   | I  | Dead-time adjustment                                                                                                     |  |  |  |  |  |

| 1,32,33        | NC   | NC | Leave floating                                                                                                           |  |  |  |  |  |

*I* = *Input*, *O* = *Output*, *P* = *Power*, *G* = *Ground*, *NC* = *No Connect*

# Ordering information

| Ordering No. | Description           |

|--------------|-----------------------|

| CGC02002     | QFN9*9, 2000 pcs/reel |

CLOUDSEMI 云 镓 半 导 体

# **Table of Contents**

| Gei     | neral description                                                                                                                                                     | 1                          |

|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|

| Fea     | atures                                                                                                                                                                | 1                          |

| Тур     | pical applications                                                                                                                                                    | 1                          |

| Pin     | configuration and functions                                                                                                                                           | 2                          |

| Orc     | dering information                                                                                                                                                    | 3                          |

| Tab     | ble of contents                                                                                                                                                       | 4                          |

| 1       | Absolute maximum ratings                                                                                                                                              | 5                          |

| 2       | Recommended operating conditions                                                                                                                                      | 6                          |

| 3       | Thermal characteristics                                                                                                                                               | 6                          |

| 4       | Electrical characteristics                                                                                                                                            | 7                          |

|         | 4.1 Driver                                                                                                                                                            | 7                          |

|         | 4.2 GaN power transistor                                                                                                                                              | 8                          |

|         | 4.3 Switching characteristics                                                                                                                                         | 9                          |

| 5       | Block diagram                                                                                                                                                         | 10                         |

| 6       | Switching waveforms                                                                                                                                                   | 10                         |

| 7       | Electrical characteristics diagrams                                                                                                                                   | 12                         |

| 8       | Function description                                                                                                                                                  |                            |

|         |                                                                                                                                                                       | 14                         |

|         | 8.1 Under Voltage Lock Out (UVLO)                                                                                                                                     |                            |

|         | •                                                                                                                                                                     | 14                         |

|         | 8.1 Under Voltage Lock Out (UVLO)                                                                                                                                     | 14<br>14                   |

|         | 8.1 Under Voltage Lock Out (UVLO)                                                                                                                                     | 14<br>14<br>15             |

| 9       | 8.1 Under Voltage Lock Out (UVLO)<br>8.2 Input and Output Logic<br>8.3 Programmable Deadtime (DT pin)                                                                 | 14<br>14<br>15<br>16       |

| 9<br>10 | <ul> <li>8.1 Under Voltage Lock Out (UVLO)</li> <li>8.2 Input and Output Logic</li> <li>8.3 Programmable Deadtime (DT pin)</li> <li>8.4 Bootstrap structure</li></ul> | 14<br>14<br>15<br>16<br>17 |

## 1 Absolute maximum ratings

At  $T_j = 25$  °C unless otherwise specified. Continuous application of maximum ratings can deteriorate product lifetime. For further information, contact CloudSemi sales office.

| Parameters                                    | Symbols                    | Min.  | Max.                   | Units | Notes/Test Conditions                          |

|-----------------------------------------------|----------------------------|-------|------------------------|-------|------------------------------------------------|

| High-side common mode voltage                 | Vsw                        | -650  | 650                    | V     |                                                |

| Driver Supply Voltage                         | VDD to SGND                | -0.3  | 24                     | V     |                                                |

| Regulator Output Voltage                      | VDDL to PGND, VDDH to OUTb | -0.3  | 7                      | V     |                                                |

| Different Ground Voltage                      | SGND to PGND               | -5    | 5                      | V     |                                                |

| Input Signal Voltage                          | HIN, LIN, EN, DT to SGND   | -0.3  | V <sub>VDD</sub> +0.3  | V     |                                                |

| Input Signal Voltage,<br>transient for 50ns   | HIN, LIN, EN, DT to SGND   | -5    | Vvdd+0.3               | V     |                                                |

| Driver Output Voltage                         | GL to PGND                 | -0.3  | V <sub>VDDL</sub> +0.3 | V     |                                                |

| Enter edipat reliage                          | GH to OUTb                 | -0.3  | V <sub>VDDH</sub> +0.3 |       |                                                |

| Driver Output Voltage,                        | GL to PGND                 | -2    | 7                      | V     |                                                |

| transient for 50ns                            | GH to OUTb                 | -2    | 7                      | •     |                                                |

| GaN drain-source voltage                      | VDS, max                   | -     | 650                    | V     | $V_{GS}=0~V,~I_{D}=10~\mu A$                   |

| Drain-source voltage transient <sup>1</sup>   | VDS, transient             | -     | 750                    | V     | $V_{GS} = 0 V, V_{DS} = 750 V$                 |

| Continuous current, drain-<br>source          | ID                         | -     | 10                     | А     | T <sub>c</sub> = 25 °C                         |

| Pulsed current, drain-<br>source <sup>2</sup> | I <sub>D, pulse</sub>      | -     | 20                     | А     | T <sub>c</sub> = 25 °C; V <sub>GS</sub> = 6 V  |

| Pulsed current, drain-<br>source <sup>2</sup> | ID, pulse                  | -     | 10                     | А     | T <sub>c</sub> = 125 °C; V <sub>GS</sub> = 6 V |

| Operating temperature                         | Тј                         | -40   | +150                   | °C    |                                                |

| Storage temperature                           | T <sub>stg</sub>           | -55   | +150                   | °C    |                                                |

| Electrostatia Discharza                       | HBM (all pins)             | -3000 | 3000                   | V     |                                                |

| Electrostatic Discharge                       | CDM                        | -1000 | 1000                   | V     |                                                |

#### Notes

1.  $V_{DS, transient}$  is intended for surge rating during non-repetitive events,  $t_{Pulse}$  < 1  $\mu s$ .

2. Pulse width = 10  $\mu$ s.

# 2 Recommended operating conditions

At  $T_j = 25$  °C unless otherwise specified. Continuous application of maximum ratings can deteriorate product lifetime. For further information, contact CloudSemi sales office.

| Parameters                       | Symbols                  | Min.   | Max.             | Units | Notes/Test Conditions |

|----------------------------------|--------------------------|--------|------------------|-------|-----------------------|

| High-side Common Mode<br>Voltage | V <sub>SW</sub>          | 0      | 600              | V     |                       |

| Driver Supply Voltage            | VDD to SGND              | 10     | 18               | V     |                       |

| Driver Output Voltage            | GL to PGND<br>GH to OUTb | 0<br>0 | Vvddl<br>Vvddh   | V     |                       |

| Input Signal Voltage             | HIN, LIN, EN, DT to SGND | 0      | V <sub>VDD</sub> | V     |                       |

| High voltage bus                 | HV to SENSE              | 0      | 520              | V     |                       |

| Operating temperature            | Tj                       | -40    | +130             | °C    |                       |

| Ambient Temperature              | Та                       | -40    | +125             | °C    |                       |

# **3** Thermal characteristics

| Parameters                       | Symbols                   |      | Values |      | Units | Notes/Test Conditions |

|----------------------------------|---------------------------|------|--------|------|-------|-----------------------|

| Farameters                       | Symbols                   | Min. | Тур.   | Max. | Units | Notes/Test Conditions |

| Thermal resistance junction to   |                           |      |        |      |       |                       |

| each GaN transistor exposed pad, | Rth(J-CB)                 | -    | -      | 2    | °C/W  |                       |

| typical                          |                           |      |        |      |       |                       |

| Thermal resistance junction-to-  | <b>D</b> <sub>4</sub> (1) |      |        | 18   | °C/W  |                       |

| ambient                          | R <sub>th(J-A)</sub>      | -    | -      | 10   | -0/00 |                       |

| Reflow soldering temperature     | T <sub>sold</sub>         | -    | -      | 260  | °C    | MSL3                  |

## 4 Electrical characteristics

### 4.1 Driver

At VDD=12V,  $T_j$  = 25 °C, unless specified otherwise.

| _                                  |                                                  | Values        |      |      |       |                                                         |  |

|------------------------------------|--------------------------------------------------|---------------|------|------|-------|---------------------------------------------------------|--|

| Parameters                         | Symbols                                          | Min. Typ. Max |      | Max. | Units | Notes/Test Conditions                                   |  |

| Driver Power Supply                |                                                  | 1             |      |      |       | I                                                       |  |

| V <sub>DD</sub> quiescent current  | IVDDQ                                            | -             | 0.42 | -    | mA    | HIN = LIN = 0 V                                         |  |

| V <sub>DD</sub> operating current  | Ivddo                                            | -             | 1    | -    | mA    | HV = SW = 0V, BOOT = 12V, 1<br>= 500kHz                 |  |

| BOOT quiescent current             | I <sub>BOOTQ</sub>                               | -             | 0.55 | -    | mA    |                                                         |  |

| BOOT operating current             | Івоото                                           | -             | 1.2  | -    | mA    | HV = SW = 0V, BOOT = 12V,<br>= 500kHz                   |  |

| BOOT UVLO state quiescent current  | IBOOTQ_OFF                                       | -             | 0.3  | -    | mA    | BOOT-SW = 7V                                            |  |

| VDD UVLO rising threshold          | Vvdd_on                                          | 8.1           | 8.4  | 8.8  | V     |                                                         |  |

| VDD UVLO falling threshold         | Vvdd_off                                         | 7.5           | 7.8  | 8.1  | V     |                                                         |  |

| VDD UVLO hysteresis                | VVDD_HYS                                         | 0.4           | 0.6  | -    | V     |                                                         |  |

| BOOT UVLO rising threshold         | VBOOT_ON                                         | 8.1           | 8.4  | 8.8  | V     |                                                         |  |

| BOOT UVLO falling threshold        | VBOOT_OFF                                        | 7.5           | 7.8  | 8.1  | V     |                                                         |  |

| BOOT UVLO hysteresis               | VBOOT_HYS                                        | 0.4           | 0.6  | -    | V     |                                                         |  |

| Input Logic                        | •                                                |               |      | •    |       |                                                         |  |

| Input pin pull-down resistance     | Rhin_pd,<br>R <sub>lin_pd</sub>                  | -             | 200  | -    | kΩ    | HIN = LIN = 3V                                          |  |

| Enable pin pull-down resistance    | R <sub>EN_PD</sub>                               | -             | 200  | -    | kΩ    | EN = 3V                                                 |  |

| Input pin high logic bias current  | Ihin_h, Ilin_h                                   | -             | 20   | -    | μA    | HIN = LIN = 5V                                          |  |

| Enable pin high logic bias current | I <sub>EN_H</sub>                                | -             | 20   | -    | μA    | EN = 5V                                                 |  |

| Logic high input threshold         | Vhin_h,<br>Vlin_h, Ven_h                         | 1.7           | 2.1  | 2.5  | V     |                                                         |  |

| Logic low input threshold          | Vhin_l,<br>Vlin_l, Ven_l                         | 0.9           | 1.2  | 1.5  | V     |                                                         |  |

| Logic input hysteresis             | Vhin_hys,<br>Vlin_hys,<br>Ven_hys                | 0.7           | 0.9  | -    | v     |                                                         |  |

| Driver Output Characteristic       |                                                  |               |      |      |       | ·                                                       |  |

| Regulator Output Voltage           | V <sub>VDDL,</sub><br>V <sub>VDDH</sub> -Vsw     | 5.7           | 6    | 6.3  | V     | C <sub>VDDL</sub> = 100nF, C <sub>VDDH-SW</sub> = 100nF |  |

| Regulator UVLO rising threshold    | Vvddh_on,<br>Vvddl_on                            | 4.3           | 4.5  | 4.7  | v     |                                                         |  |

| Regulator UVLO falling threshold   | Vvddh_off,<br>Vvddl_off                          | 3.8           | 4    | 4.2  | v     |                                                         |  |

| Regulator UVLO hysteresis          | V <sub>VDDH_HYS</sub> ,<br>V <sub>VDDL_HYS</sub> | 0.4           | 0.5  | -    | V     |                                                         |  |

### CGC02002 DATASHEET 650V Half-Bridge GaN Transistors with Gate Driver

| Driver output pull-down resistance | Rlsnk,<br>Rhsnk                          | - | 1      | - | Ω |  |

|------------------------------------|------------------------------------------|---|--------|---|---|--|

| Driver output pull-up resistance   | R <sub>LSRC</sub> ,<br>R <sub>HSRC</sub> | - | 51     | - | Ω |  |

| Output peak source current         | Ilsrc_pk,<br>I <sub>hsrc_pk</sub>        | - | 2<br>2 | - | A |  |

| Output peak sink current           | I <sub>lsnk_pk</sub> ,<br>Ihsnk_pk       | - | 4<br>4 | - | A |  |

### 4.2 GaN power transistor

At  $T_j = 25$  °C, unless specified otherwise.

| <b>D</b>                         |                      |          | Values   |      |       |                                                                      |  |

|----------------------------------|----------------------|----------|----------|------|-------|----------------------------------------------------------------------|--|

| Parameters                       | Symbols              | Min.     | Тур.     | Max. | Units | Notes/Test Conditions                                                |  |

| Low-side / High-side GaN power   | FET static char      | acterist | ics      |      |       | ·                                                                    |  |

| Drain-source voltage             | V <sub>DS, max</sub> | -        | -        | 650  | V     | $V_{GS} = 0 V; I_D = 10 \mu A$                                       |  |

|                                  |                      |          |          | 20   |       | V <sub>DS</sub> = 650 V; V <sub>GS</sub> = 0 V;                      |  |

| Drain agurag lagkaga gurrant     | la a a               | -        |          | 20   |       | T <sub>j</sub> = 25 °C                                               |  |

| Drain-source leakage current     | IDSS                 |          | <u> </u> |      | μA    | V <sub>DS</sub> = 650 V; V <sub>GS</sub> = 0 V;                      |  |

|                                  |                      | -        | 6        | -    |       | T <sub>j</sub> = 150 °C                                              |  |

|                                  |                      | 1.0      | 47       | 25   |       | $I_D = 6.6 \text{ mA}; V_{DS} = V_{GS};$                             |  |

|                                  |                      | 1.2      | 1.7      | 2.5  | v     | T <sub>j</sub> = 25 °C                                               |  |

| Gate threshold voltage           | VGS(th)              |          | 1.7      | -    | V     | $I_D = 6.6 \text{ mA}; V_{DS} = V_{GS};$                             |  |

|                                  |                      | -        |          |      |       | T <sub>j</sub> = 125 °C                                              |  |

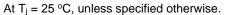

|                                  | R <sub>DS(on)</sub>  | -        | 140      | 190  | mΩ    | V <sub>GS</sub> = 6 V; I <sub>D</sub> = 6 A; T <sub>j</sub> = 25 °C  |  |

| Drain-source on-state resistance |                      | -        | 250      | -    |       | V <sub>GS</sub> = 6 V; I <sub>D</sub> = 6 A; T <sub>j</sub> = 150 °C |  |

| Low-side / High-side GaN power   | FET dynamic c        | haracte  | ristics  |      |       | ·                                                                    |  |

| Total Gate charge                | Q <sub>G</sub>       | -        | 2.8      | -    | nC    | $V_{GS} = 0$ to 6 V; $V_{DS} = 400$ V; $I_D =$                       |  |

| Total Gate charge                | QG                   | -        | 2.0      | -    | nc    | 6 A                                                                  |  |

| Output charge                    | Qoss                 | -        | 25       | -    | nC    |                                                                      |  |

| Output Capacitance Stored        | E <sub>oss</sub>     | _        | 3.6      | -    | μJ    | $V_{GS} = 0 V; V_{DS} = 0 to 400 V$                                  |  |

| Energy                           | Loss                 | _        | 5.0      | -    | μυ    | $V_{\rm GS} = 0.0, V_{\rm DS} = 0.00400.0$                           |  |

| Output capacitance               | Coss                 | -        | 30       | -    | pF    |                                                                      |  |

| Effective output capacitance,    | C ( )                | -        | 41       | -    | pF    | V <sub>GS</sub> = 0 V; V <sub>DS</sub> = 0 to 400 V                  |  |

| energy related <sup>1</sup>      | C <sub>o(er)</sub>   | -        | 41       | -    | рг    | $v_{\rm GS} = 0 v, v_{\rm DS} = 0 t0 400 v$                          |  |

| Effective output capacitance,    | C                    |          | 63       | -    | ьE    | V <sub>GS</sub> = 0 V; V <sub>DS</sub> = 0 to 400 V                  |  |

| time related <sup>2</sup>        | C <sub>o(tr)</sub>   | -        | 03       | -    | pF    | $v_{\rm GS} = 0$ V, $v_{\rm DS} = 0$ to 400 V                        |  |

| Reverse recovery charge          | Qrr                  | -        | 0        | -    | nC    |                                                                      |  |

| Peak reverse recovery current    | I <sub>rrm</sub>     | -        | 0        | -    | А     |                                                                      |  |

#### Notes

1.  $C_{o(er)}$  is the fixed capacitance that gives the same stored energy as  $C_{OSS}$  while  $V_{DS}$  is rising from 0 to 400 V.

2.  $C_{o(tr)}$  is the fixed capacitance that gives the same charging time as  $C_{OSS}$  while  $V_{DS}$  is rising from 0 to 400 V.

# 4.3 Switching characteristics

| Parameters                         | Ourseland a         | Values |      |      |       | Nata - Tract Oan ditions           |  |  |  |

|------------------------------------|---------------------|--------|------|------|-------|------------------------------------|--|--|--|

|                                    | Symbols             | Min.   | Тур. | Max. | Units | Notes/Test Conditions              |  |  |  |

| Low-side / High-side GaN power FET |                     |        |      |      |       |                                    |  |  |  |

| Turn-on delay time                 | t <sub>d(on)</sub>  | -      | 70   | -    | ns    | 111/ 4001/                         |  |  |  |

| Turn-on rise time                  | t <sub>r(on)</sub>  | -      | 15   | -    | ns    | HV = 400V<br>V <sub>GS</sub> = 6 V |  |  |  |

| Turn-off delay time                | t <sub>d(off)</sub> | -      | 70   | -    | ns    | v <sub>GS</sub> = 6 v<br>Ip = 6 A  |  |  |  |

| Turn-off fall time                 | t <sub>f(off)</sub> | -      | 15   | -    | ns    | D = 0 A                            |  |  |  |

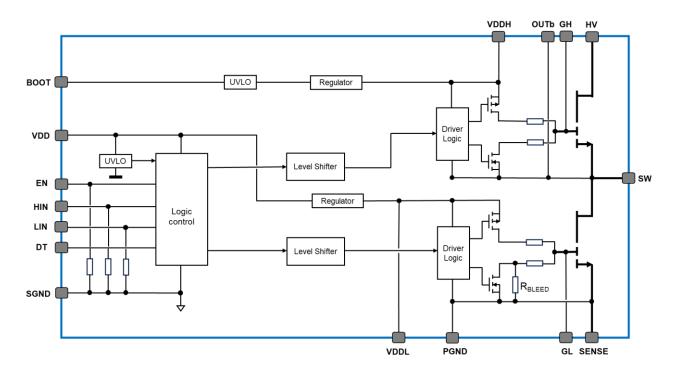

## 5 Block diagram

## 6 Switching waveforms

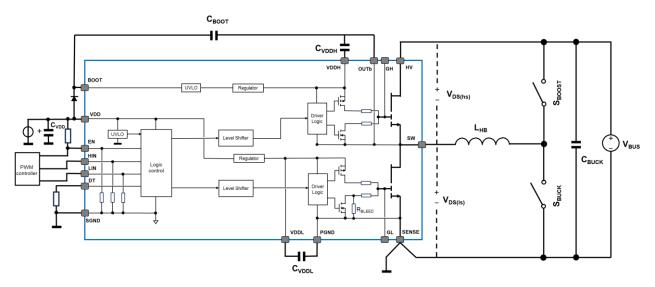

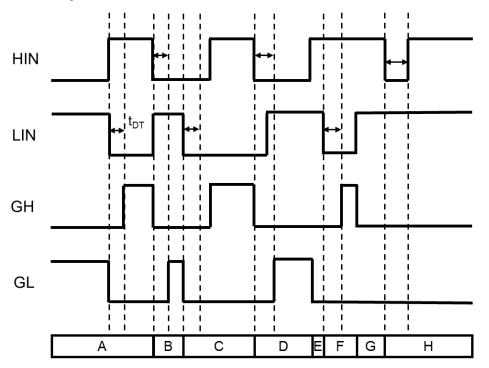

Figure 6.1 shows the circuit used to measure the GaN power FET switching parameters. The circuit is operated as a double-pulse tester. Consult external references for double-pulse tester details. The circuit is placed in the boost configuration to measure the low-side GaN switching parameters. The circuit is placed in the buck configuration to measure the high-side GaN switching parameters. The GaN FET not being measured in each configuration (high-side in the boost and low-side in the buck) acts as the double-pulse tester diode and circulates the inductor current in the off-state, third-quadrant conduction mode. Table 6.1 shows the details for each configuration.

### CGC02002 DATASHEET 650V Half-Bridge GaN Transistors with Gate Driver

#### Table 6.1 GaN power FET switching parameters test circuit configuration details

| Configuration | GaN FET<br>under test | GaN FET Acting<br>as diode | SBOOST | SBUCK  | V <sub>LIN</sub>         | V <sub>HIN</sub>         |

|---------------|-----------------------|----------------------------|--------|--------|--------------------------|--------------------------|

| Boost         | Low-side              | High-side                  | Closed | Open   | Double-pulse<br>waveform | 0V                       |

| Buck          | High-side             | Low-side                   | Open   | Closed | 0V                       | Double-pulse<br>waveform |

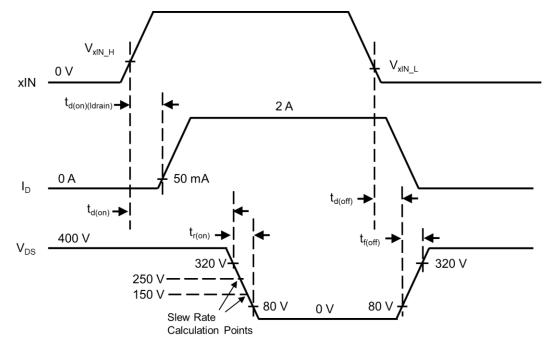

Figure 6.2 shows the GaN power FET switching parameters.

The GaN power FET turn-on transition has three timing components: drain-current turn-on delay time, turnon delay time, and turn-on rise time. Note that the turn-on rise time is the same as the VDS 80% to 20% fall time.

The GaN power FET turn-off transition has two timing components: turn-off delay time, and turn-off fall time. Note that the turn-off fall time is the same as the VDS 20% to 80% rise time.

The turn-on slew rate is measured over a smaller voltage delta (100 V) compared to the turn-on rise time voltage delta (240 V) to obtain a faster slew rate which is useful for EMI design.

Figure 6.2 GaN power FET switching parameters

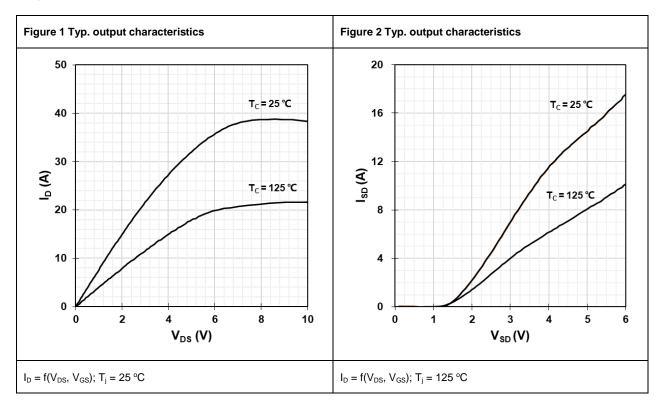

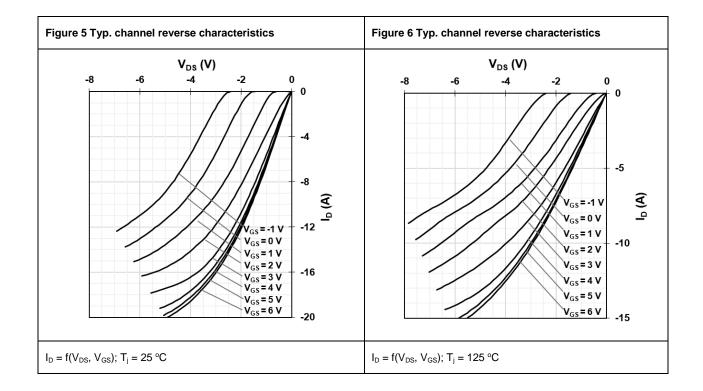

## 7 Electrical characteristics diagrams

CLOUDSEMI 云 镓 半 导 体

### 8 Function description

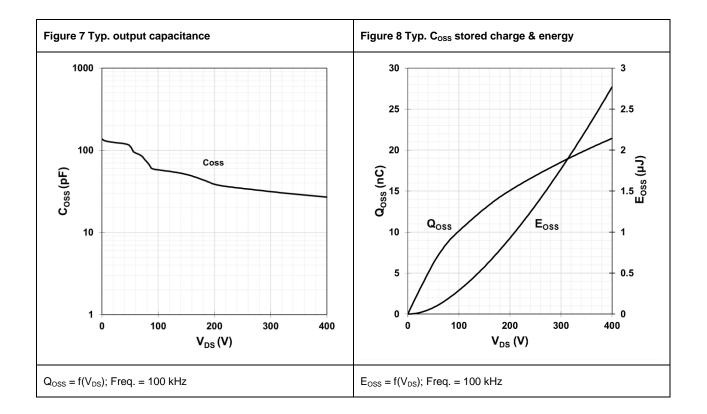

### 8.1 Under Voltage Lock Out (UVLO)

The CGC02002 has internal under voltage lock out (UVLO) protections on low side and high side power supply blocks. The driver output is held low by an active clamp circuit when the supply voltage of VDD or BOOT is lower than  $V_{VDD_ON}$  at power-up status or lower than  $V_{VDD_OFF}$  after power-up, regardless of the status of the input pins.

The 0.5V hysteresis ( $V_{VDD_HYS}$ ) on VDD and BOOT ULVO protections are provided prevent chatter noise from VDD supply and allow small drops in supply power which are usually happened in startup. The recovery propagation time of  $V_{VDDL}$  is about 1us when  $V_{VDD}$  voltage fall from more than  $V_{VDD_ON}$  to some value between  $V_{VDD_OFF}$  and  $V_{VDD_POR}$  and then raise to more than  $V_{VDD_ON}$ .

A not less than 100nF ceramic capacitor must be used on VDDL and VDDH to normally operate.

Figure 8.1 UVLO Diagram

### 8.2 Input and Output Logic

The CGC02002 an advanced system-in-package (SIP) power ICs, consisting of gate driver and two 650-V enhancement-mode GaN power transistors in half-bridge configuration with dead-time control. The EN pin should be logic high to keep the driver operating normally.

| Input Pins |     |     | Output Pins |     | Note                                         |

|------------|-----|-----|-------------|-----|----------------------------------------------|

| EN         | LIN | HIN | LS          | HS  | Note                                         |

| L or O     | Х   | х   | OFF         | OFF |                                              |

| н          | L   | L   | OFF         | OFF |                                              |

| н          | L   | Н   | OFF         | ON  |                                              |

| н          | Н   | L   | ON          | OFF |                                              |

| Н          | Н   | Н   | OFF         | OFF | The input signal is later than VDD power up. |

Table 8.1 Inputs truth table (applicable when device is not in UVLO)

**Notes:** H = Logic High; L = Logic Low; O = Left Open; X = Irrelevant.

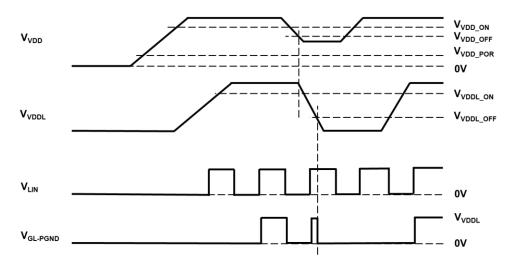

### 8.3 Programmable Deadtime (DT pin)

The CGC02002 has a programmable deadtime control function by placing a resistor,  $R_{DT}$ , between the DT pin and SGND. There are three statuses of deadtime program.

1) While  $R_{DT}$  is lower than  $20k\Omega$  or higher than  $250k\Omega$ , the deadtime duration ( $t_{DT}$ ) is set to 20ns.

2) While  $R_{DT}$  is in range of 20k $\Omega$  to 100k $\Omega$ , the  $t_{DT}$  can be determined from Equation 1, where  $R_{DT}$  is in k $\Omega$  and  $t_{DT}$  in ns:

$$t_{DT} \approx 1 \times R_{DT} \tag{1}$$

3) While  $R_{DT}$  is in range of 100 k $\Omega$  to 250k $\Omega$ , the deadtime duration (t<sub>DT</sub>) is set to 100ns.

The recommended value of  $R_{DT}$  is between from  $1k\Omega$  to  $200k\Omega$ . It is also recommended to parallel a ceramic capacitor, for example 1nF, with  $R_{DT}$  to achieve better noise immunity.

The programmed deadtime is activated by the input signal's falling edge to prevent shoot-through when the device is designed in an application of high side and low side driver. The details of input and output logic with deadtime are shown as Figure 8.2:

Figure 8.2 Input and Gate Logic with the Programmed Deadtime

| Conditions                                | Results                                                         |  |  |  |

|-------------------------------------------|-----------------------------------------------------------------|--|--|--|

| A: HIN goes high, and LIN goes low.       | GL goes low immediately, then GH goes high after the            |  |  |  |

| A. This goes high, and Line goes low.     | programmed deadtime which is assigned at LIN goes low.          |  |  |  |

| B: HIN goes low, and LIN goes high.       | GH goes low immediately, then GL goes high after the            |  |  |  |

| b. This goes low, and Line goes high.     | programmed deadtime which is assigned at HIN goes low.          |  |  |  |

| C: LIN goes low, then HIN goes high       | GL goes low immediately, then GH goes high immediately when     |  |  |  |

| after deadtime.                           | HIN goes high.                                                  |  |  |  |

| D: HIN goes low, then LIN goes high       | CIL sees low immediately, then CL sees high often deadtime      |  |  |  |

| before deadtime.                          | GH goes low immediately, then GL goes high after deadtime.      |  |  |  |

| E: HIN goes high, LIN is still high.      | GL goes low immediately, and GH keeps low.                      |  |  |  |

| F: HIN is still high, LIN goes low.       | GH goes high after deadtime while LIN is low, and GL keeps low. |  |  |  |

| G: HIN is still high, LIN goes high after | GH goes low immediately, and GL keeps low.                      |  |  |  |

| deadtime.                                 |                                                                 |  |  |  |

| H: HIN goes low then goes high before     |                                                                 |  |  |  |

| deadtime while LIN is still high.         | GH keeps low and GL keeps low because deadtime control.         |  |  |  |

### 8.4 Bootstrap structure

A bootstrap circuitry is typically used to supply the high-voltage section. The CGC02002 integrates this structure to reduce the external components.

The Bootstrap integrated circuit is connected to VDD pin and is driven synchronously with the low-side driver.

The use of an external bootstrap diode in parallel to the integrated structure is possible, in particular if the operating frequency is approximately higher than 500 kHz.

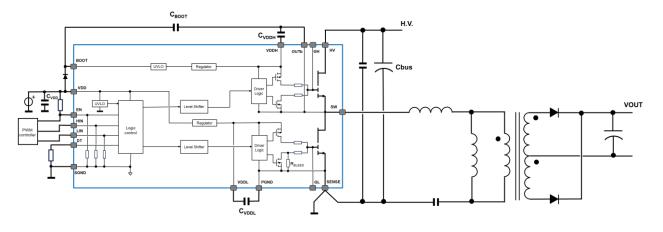

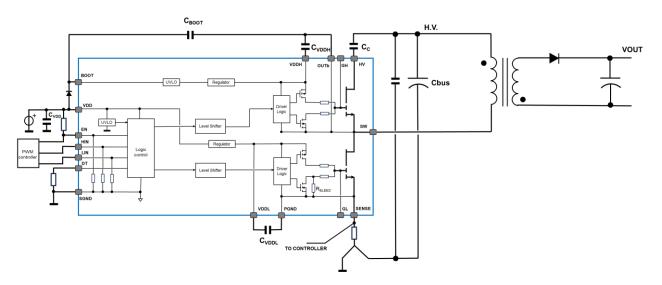

# **9** Typical application diagrams

Figure 8.1 Typical application diagram: Resonant LLC converter

Figure 8.2 Typical application diagram: Active clamp flyback

# 10 Package outlines

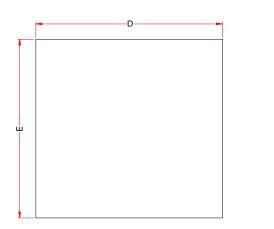

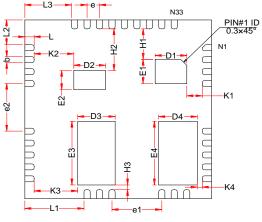

TOP VIEW

SIDE VIEW

A1— A2

BOTTOM VIEW

|    | MIN      | MID   | MAX   |

|----|----------|-------|-------|

| А  | 0.700    | 0.750 | 0.800 |

| A1 | 0.203REF |       |       |

| A2 | 0        | 0.02  | 0.05  |

| b  | 0.250    | 0.300 | 0.350 |

| D  | 9.00BSC  |       |       |

| D1 | 1.425    | 1.525 | 1.625 |

| D2 | 1.425    | 1.525 | 1.625 |

| D3 | 1.700    | 1.860 | 1.960 |

| Е  | 9.00BSC  |       |       |

| E1 | 1.120    | 1.220 | 1.320 |

| E2 | 0.860    | 0.960 | 1.060 |

| E3 | 3.100    | 3.200 | 3.300 |

| E4 | 3.100    | 3.200 | 3.300 |

| е  | 0.600BSC |       |       |

| e1 | 2.400BSC |       |       |

| e2 | 2.400BSC |       |       |

| K1 | 0.644    | 0.744 | 0.844 |

| K2 | 1.810    | 1.910 | 2.010 |

| K3 | 2.000    | 2.100 | 2.200 |

| K4 | 0.140    | 0.240 | 0.340 |

| L  | 0.400    | 0.450 | 0.500 |

| L1 | 2.850REF |       |       |

| L2 | 1.250REF |       |       |

| L3 | 2.250REF |       |       |

| H1 | 1.434    | 1.534 | 1.634 |

| H2 | 2.000    | 2.100 | 2.200 |

| H3 | 0.140    | 0.240 | 0.340 |

| Row   | Description  | Example    |

|-------|--------------|------------|

| Row 1 | Device name  | CGXXXXXXXX |

| Row 2 | ASSY lot No. | XXXXXXXX   |

| Row 3 | Year & Week  | YXWX       |

# **11 Revision history**

Major changes since the last revision

| Revision | Date      | Description of changes |

|----------|-----------|------------------------|

| 0.5      | 2023-5-5  | 0.5 version release    |

| 1.0      | 2023-12-5 | 1.0 version release    |