### Half-Bridge GaN Gate Driver with Integrated Bootstrap Diode

#### **General description**

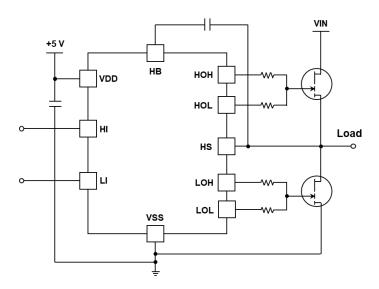

The CGHB2202 is designed to drive both the highside and the low-side enhancement-mode (Emode) GaN FETs in a synchronous buck, boost, half-bridge or full-bridge configuration. The driver has an integrated 100-V bootstrap diode and independent inputs for the high-side and low-side outputs for maximum control flexibility. The highside bias voltage is generated using a bootstrap technique and is internally clamped at 5 V, which prevents the gate voltage from exceeding the maximum gate-source voltage rating of E-mode GaN FETs. The inputs of the CGHB2202 are TTL logic compatible and can withstand input voltages up to 15 V regardless of the VDD voltage. The CGHB2202 has split-gate outputs, providing flexibility to adjust the turn-on and turn-off strength independently.

The CGHB2202 features fast propagation times and excellent minimum input pulse to ensure high-frequency applications. The CGHB2202 is available in a 12-pin WLCSP package that offers a compact footprint and minimized package inductance.

#### **Features**

- Independent high-side and low-side TTL logic Inputs

- 1.2-A peak source, 5-A sink current

- High-side floating bias voltage rail operates up to 100 VDC

- Split outputs for adjustable turn-on, turn-off strength

- Fast propagation times (8-ns typical)

- Excellent minimum input pulse (8-ns typical)

- · UVLO and over-temperature protection

- Single 5-V supply voltage

- WLCSP package with low parasitic inductance

#### **Typical applications**

- · Half and full-bridge converters

- · Synchronous buck converters

- Motor drive

- · Class-D audio amplifiers

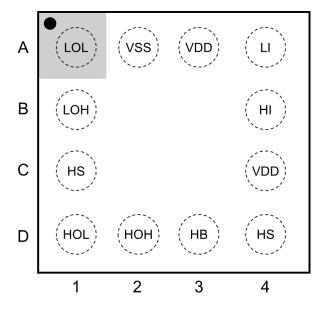

# Pin configuration and functions

| Pin#                | Name     | I/O <sup>2</sup> | Description                                                                |  |  |  |

|---------------------|----------|------------------|----------------------------------------------------------------------------|--|--|--|

| A1                  | LOL      | 0                | Low-side gate driver sink-current output: connect to the gate of low-      |  |  |  |

|                     |          |                  | side GaN FET. A gate resistor can be used to adjust the turn-off speed.    |  |  |  |

| A2                  | VSS      | G                | Ground return: all signals are referenced to this ground.                  |  |  |  |

| A3, C4 <sup>1</sup> | VDD      | Р                | 5-V positive gate drive supply: locally decouple to VSS using low          |  |  |  |

| 710, 04             | VDD      | •                | ESR/ESL capacitor located as close as possible to the IC.                  |  |  |  |

| A4                  | LI       | I                | Low-side driver control input.                                             |  |  |  |

| R1                  | B1 LOH O |                  | Low-side gate driver source-current output: connect to the gate of low-    |  |  |  |

| 51                  |          |                  | side GaN FET. A gate resistor can be used to adjust the turn-on speed.     |  |  |  |

| B4                  | Н        | I                | High-side driver control input.                                            |  |  |  |

| C1, D4 <sup>1</sup> | HS       | Р                | High-side GaN FET source connection: connect to the bootstrap              |  |  |  |

| 01, 04              | 110      | F                | capacitor negative terminal and the source of the high-side GaN FET.       |  |  |  |

| D1                  | HOL      | 0                | High-side gate driver turn-off output: connect to the gate of high-side    |  |  |  |

|                     | TIOL     | U                | GaN FET. A gate resistor can be used to adjust the turn-off speed.         |  |  |  |

| D2                  | НОН      | 0                | High-side gate driver turn-on output: connect to the gate of high-side     |  |  |  |

| D2                  | D2 HOH O |                  | GaN FET. A gate resistor can be used to adjust the turn-on speed.          |  |  |  |

|                     |          |                  | High-side gate driver bootstrap rail: connect the positive terminal of the |  |  |  |

| D3                  | НВ       | Р                | bootstrap capacitor to HB and the negative terminal to HS. The             |  |  |  |

|                     |          |                  | bootstrap capacitor must be placed as close as possible to the IC.         |  |  |  |

<sup>1.</sup> A3 and C4, C1 and D4 are internally connected.

<sup>2.</sup> I = Input, O = Output, P = Power, G = Ground, NC = No Connect

### **Table of Contents**

| Ge  | neral description                                             | 1   |

|-----|---------------------------------------------------------------|-----|

| Fea | atures                                                        | 1   |

| Тур | pical applications                                            | 1   |

| Pin | configuration and functions                                   | 2   |

| Tak | ble of contents                                               | 3   |

| 1   | Absolute maximum ratings                                      | 4   |

| 2   | Recommended operating conditions                              | 4   |

| 3   | Thermal characteristics                                       | 4   |

| 4   | ESD ratings                                                   | 4   |

| 5   | Electrical characteristics                                    | 5   |

|     | 5.1 Static characteristics                                    | 5   |

|     | 5.2 Switching characteristics                                 | 6   |

| 6   | Block diagram                                                 | 7   |

| 7   | Function description                                          | 7   |

|     | 7.1 Input and output                                          | 7   |

|     | 7.2 Start-up and UVLO                                         | 7   |

|     | 7.3 HS negative voltage and bootstrap supply voltage clamping | 8   |

|     | 7.4 Level shift                                               | 8   |

|     | 7.5 Truth table                                               | 8   |

|     | 7.6 Typical testing waveforms                                 | 8   |

| 8   | Layout guidelines                                             | 8   |

| 9   | Package information                                           | .10 |

| 10  | Tape and reel information                                     | 11  |

| 11  | Revision history                                              | 12  |

# 1 Absolute maximum ratings

At  $T_j = 25$  °C unless otherwise specified. Continuous application of maximum ratings can deteriorate product lifetime. For further information, contact CloudSemi sales office.

| Symbols          | Parameters                      | Min.      | Max.      | Units |

|------------------|---------------------------------|-----------|-----------|-------|

| VDD to VSS       | Driver supply voltage           | -0.3      | 6         | V     |

| HB to HS         | High-side bootstrap Voltage     | -0.3      | 6         | V     |

| LI or HI input   | Input signal voltage            | -0.3      | 18        | V     |

| LOH, LOL output  | Low-side driver output voltage  | -0.3      | VDD + 0.3 | V     |

| HOH, HOL output  | High-side driver output voltage | VHS - 0.3 | VHB + 0.3 | V     |

| HS to VSS        | High-side common-mode voltage   | -5        | 100       | V     |

| HB to VSS        | Bootstrap voltage               | 0         | 106       | V     |

| TJ               | Operating junction temperature  |           | 150       | °C    |

| T <sub>stg</sub> | Storage temperature             | -55       | 150       | °C    |

### 2 Recommended operating conditions

| Symbols         | Parameters            | Min.    | Тур. | Max.      | Units |

|-----------------|-----------------------|---------|------|-----------|-------|

| V <sub>DD</sub> | Supply voltage        | 4.75    | 5    | 5.25      | V     |

| LI or HI INPUT  | Input voltage         | 0       | 5    | 15        | V     |

| HS              | High Side GaN Source  | -5      |      | 90        | V     |

| НВ              | High Side GaN Gate    | VHS + 4 |      | VHS + 5.5 | V     |

| TJ              | Operating Temperature | -40     |      | 125       | °C    |

### 3 Thermal characteristics

| Symbols              | Parameters                             | Values | Units |

|----------------------|----------------------------------------|--------|-------|

| R <sub>th(J-A)</sub> | Thermal resistance junction-to-ambient | 77     | °C/W  |

### 4 ESD ratings

| Parameters           | Symbols                                                                   | Values | Units |

|----------------------|---------------------------------------------------------------------------|--------|-------|

| V(ESD) Electrostatic | Charged device model (CDM), per JEDEC specification JESD22-C101, all pins | ±500   | V     |

| discharge            | Human body model (HBM), per ANSI/ESDA/JEDEC JS-001, all pins              | ±1500  | V     |

### **5** Electrical characteristics

#### 5.1 Static characteristics

| Symbols                        | Parameters                                          | Min.  | Тур.  | Max.   | Units | Test Conditions            |

|--------------------------------|-----------------------------------------------------|-------|-------|--------|-------|----------------------------|

| DC Characteristics             |                                                     |       |       |        |       |                            |

| Ivdd,q                         | VDD Quiescent Current                               | 0.025 | 0.04  | 0.055  | mA    | HI= LI= 0V<br>VDD= VHB= 5V |

| I <sub>VDD,op</sub>            | VDD Operating Current                               |       | 0.5   | 1      | mA    | fsw= 500kHz                |

| IHB,q                          | HB Quiescent Current                                | 0.010 | 0.012 | 0.020  | mA    | HI= LI= 0V<br>VDD= VHB= 5V |

| IHB,op                         | HB Operating Current                                |       | 0.5   | 1      | mA    | fsw= 500kHz                |

| Інвs                           | HB to VSS quiescent current                         |       | 0.2   | 50     | uA    | HS= HB= 80V                |

| V <sub>DD,UVLO</sub>           | VDD rising threshold                                | 3.9   | 4     | 4.2    | V     | VDD rising                 |

| V <sub>DDH,UVLO</sub>          | VDD threshold hysteresis                            |       | 200   |        | mV    |                            |

| V <sub>HB,UVLO</sub>           | HB rising threshold                                 | 2.5   |       | 3.5    | V     |                            |

| V <sub>HBH,UVLO</sub>          | HB threshold hysteresis                             |       | 200   |        | mV    |                            |

| Тотр                           | Over temperature shutdown turn-off threshold        |       | 164   |        | °C    |                            |

| Тотр                           | Over temperature hysteresis                         |       | 20    |        | °C    |                            |

| Bootstrap Diode a              | and Clamp                                           |       |       |        |       |                            |

| V <sub>DL</sub>                | Low-current forward voltage                         | 0.1   | 0.38  | 0.57   | V     | I <sub>VDD</sub> -HB=100uA |

| V <sub>DH</sub>                | High-current forward voltage                        | 0.87  | 1     | 1.08   | V     | I <sub>VDD</sub> -HB=100mA |

| HB-HS clamp regulation voltage |                                                     | 4.5   | 5     | 5.5    | V     |                            |

| Input DC Characte              | eristics                                            | 1     | l     |        | l     |                            |

| VIR                            | HI, LI high threshold                               | 1.8   |       | 2.2    | V     |                            |

| VIF                            | HI, LI low threshold                                | 1.5   |       | 1.8    | V     |                            |

| V <sub>IHYS</sub>              | HI, LI hysteresis                                   | 0.4   |       | 0.9    | V     |                            |

| R <sub>IN+</sub>               | Positive input pull-down resistance                 | 100   | 200   | 300    | kΩ    | To GND                     |

| Output DC Charac               | cteristics                                          | 1     | l     |        | l     |                            |

| VoL                            | Low-level output voltage                            | 0.02  | 0.03  | 0.04   | V     | IHOL= ILOL= 100mA          |

| Vон                            | High-level output voltage VOH=VDD–LOH or VOH=HB–HOH | 0.1   | 0.14  | 0.16 V |       | IHOH= ILOH=<br>100mA       |

| I <sub>OH</sub>                | Peak source current                                 | 1.6   | 1.7   | 1.8    | Α     | HOH, LOH= 0 V              |

| loL                            | Peak sink current                                   | 4     | 5     | 5.5    | Α     | HOL, LOL= 5 V              |

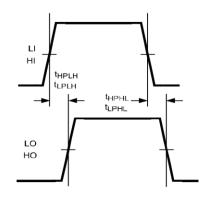

# 5.2 Switching characteristics

| Symbols           | Parameters                                        | Min. | Тур. | Max. | Units | Test Conditions                                                 |

|-------------------|---------------------------------------------------|------|------|------|-------|-----------------------------------------------------------------|

| tstart            | Startup Time, VDD rising above UVLO               | 40   | 50   | 70   | us    | LI = VDD, HI = GND,<br>VDD rising above 4.1V to<br>HO/LO rising |

| t <sub>LPHL</sub> | LO turn-off propagation delay                     | 7    | 7.8  | 9.3  | ns    | LI falling to LOL falling                                       |

| t <sub>LPLH</sub> | LO turn-on propagation delay                      | 6.6  | 7.3  | 8.4  | ns    | LI rising to LOH rising                                         |

| tнрнL             | HO turn-off propagation delay                     | 9.7  | 10.6 | 12.5 | ns    | HI falling to HOL falling                                       |

| tнецн             | HO turn-on propagation delay                      | 6.5  | 7.2  | 8    | ns    | HI rising to HOH rising                                         |

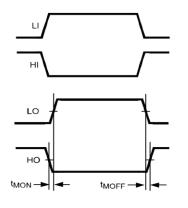

| t <sub>MON</sub>  | Delay matching LO on and HO off                   | 3.5  | 3.8  | 4.3  | ns    |                                                                 |

| tmoff             | Delay matching LO off and HO on                   | 1.1  | 1.15 | 1.2  | ns    |                                                                 |

| thrc              | HO rise time (0.5 V – 4.5 V)                      |      | 6    |      | ns    | C <sub>L</sub> = 1000 pF                                        |

| tLRC              | LO rise time (0.5 V – 4.5 V)                      |      | 6    |      | ns    | C <sub>L</sub> = 1000 pF                                        |

| t <sub>HFC</sub>  | HO fall time (0.5 V – 4.5 V)                      |      | 2.6  |      | ns    | C <sub>L</sub> = 1000 pF                                        |

| t <sub>LFC</sub>  | LO fall time (0.5 V – 4.5 V)                      |      | 2.6  |      | ns    | C <sub>L</sub> = 1000 pF                                        |

| t <sub>PW</sub>   | Minimum input pulse width that changes the output |      | 8    |      | ns    |                                                                 |

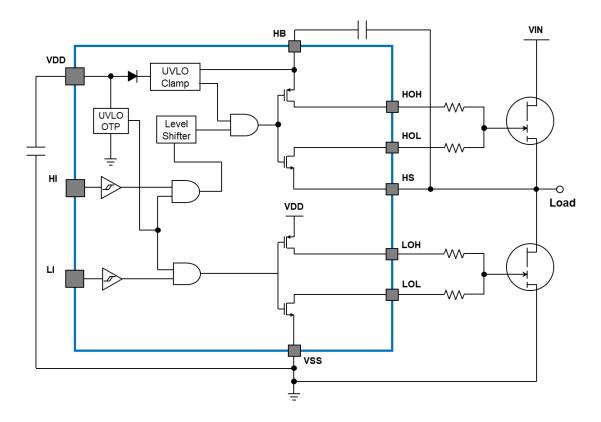

#### 6 Block diagram

### 7 Function description

#### 7.1 Input and output

The input pins of the CGHB2202 are independently controlled with TTL input thresholds and can withstand voltages up to 15V regardless of the VDD voltage. This allows the inputs to be directly connected to the outputs of an analog PWM controller with up to 12V power supply, eliminating the need for a buffer stage.

The output pulldown and pullup resistance of CGHB2202 is optimized for enhancement mode GaN FETs to achieve high frequency and efficient operation. The split outputs of the CGHB2202 offers flexibility to adjust the turn-on and turn-off speed by independently adding additional impedance in either the turn-on path and/or the turnoff path.

If the input signal for either of the two channels, HI or LI, is not used, the control pin must be tied to either VDD or VSS. These inputs must not be left floating.

#### 7.2 Start-up and UVLO

The CGHB2202 has an undervoltage lockout (UVLO) on both the VDD and bootstrap supplies. When the VDD voltage is below the threshold voltage of 3.8 V, both the HI and LI inputs are ignored, to prevent the GaN FETs from being partially turned on. Also, if there is insufficient VDD voltage, the UVLO actively pulls the LOL and HOL low. When the VDD voltage is above its UVLO threshold, but the HB to HS bootstrap voltage is below the UVLO threshold of 3.2 V, only HOL is pulled low. Both UVLO threshold voltages have 200 mV of hysteresis to avoid chattering.

#### 7.3 HS negative voltage and bootstrap supply voltage clamping

Due to the intrinsic nature of enhancement mode GaN FETs, the source-to-drain voltage of the bottom switch is usually higher than a diode forward voltage drop when the gate is pulled low. This causes negative voltage on HS pin. Moreover, this negative voltage transient may become even more pronounced due to the effects of board layout and device drain/source parasitic inductances. With high-side driver using the floating bootstrap configuration, negative HS voltage can lead to an excessive bootstrap voltage, which can damage the high-side GaN FET. The CGHB2202 solves this problem with an internal clamping circuit that prevents the bootstrap voltage from exceeding 5V typical.

#### 7.4 Level shift

The level-shift circuit is the interface from the high-side input to the high-side driver stage which is referenced to the switch node (HS). The level shift allows control of the HO output, which is referenced to the HS pin and provides excellent delay matching with the low-side driver. Typical delay matching between LO and HO is around 3ns.

#### 7.5 Truth table

| НІ | LI | нон  | HOL  | LOH  | LOL  |

|----|----|------|------|------|------|

| L  | L  | OPEN | L    | OPEN | L    |

| L  | Н  | OPEN | L    | Н    | OPEN |

| Н  | L  | Н    | OPEN | OPEN | L    |

| Н  | Н  | Н    | OPEN | Н    | OPEN |

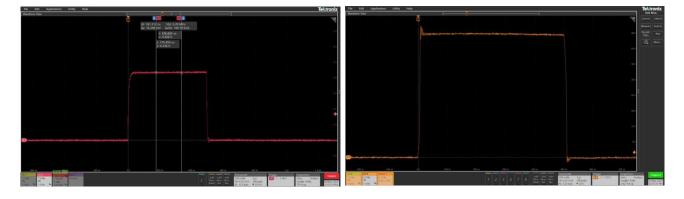

#### 7.6 Typical testing waveforms

(Left) High Side GaN Gate Waveform with EPC2088 GaN Load @ 500KHz; (Right) HS: Switch Node Waveform with EPC2088 GaN Load @ 48V to 12V DCDC Buck System, 500KHz

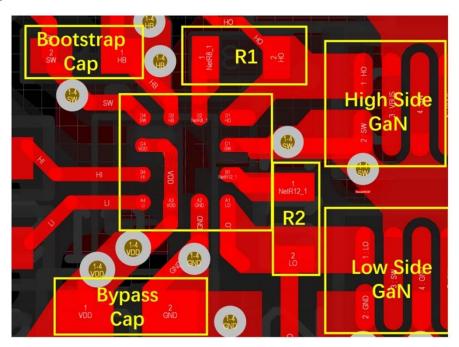

### 8 Layout guidelines

Small gate capacitance and Miller capacitance enable enhancement mode GaN FETs to operate with fast switching speed. The induced high dv/dt and di/dt, coupled with a low gate threshold voltage and limited

headroom of enhancement mode GaN FETs gate voltage, make the circuit layout crucial to the optimum performance. Following are some recommendations:

- 1. The first priority in designing the layout of the driver is to confine the high peak currents that charge and discharge the GaN FETs gate into a minimal physical area. This decreases the loop inductance and minimize noise issues on the gate terminal of the GaN FETs. The GaN FETs must be placed close to the driver.

- 2. The second high current path includes the bootstrap capacitor, the local ground referenced VDD bypass capacitor and low-side GaN FET. The bootstrap capacitor is recharged on a cycle-by-cycle basis through the bootstrap diode from the ground referenced VDD capacitor. The recharging occurs in a short time interval and involves high peak current. Minimizing this loop length and area on the circuit board is important to ensure reliable operation.

- 3. The parasitic inductance in series with the source of the high-side FET and the low-side FET can impose excessive negative voltage transients on the driver. We recommend connecting the HS pin and VSS pin to the respective source of the high-side and low-side transistors with a short and low-inductance path.

- 4. The parasitic source inductance, along with the gate capacitor and the driver pull-down path, can form an LCR resonant tank, resulting in gate voltage oscillations. An optional resistor or ferrite bead can be used to damp the ringing.

- 5. Low ESR/ESL capacitors must be connected close to the IC, between VDD and VSS pins and between the HB and HS pins to support the high peak current being drawn from VDD during turn-on of the FETs. The inductance of vias can impose excessive ringing on the IC pins.

- 6. To prevent excessive ringing on the input power bus, good decoupling practices are required by placing low ESR ceramic capacitors adjacent to the GaN FETs.

A four-layer or higher layer count board is required to reduce the parasitic inductance of the layout to achieve suitable performance. To minimize inductance and board space, resistors and capacitors in the 0201 package are used here. The gate drive power loss must be calculated to ensure an 0201 resistor will be able to handle the power level.

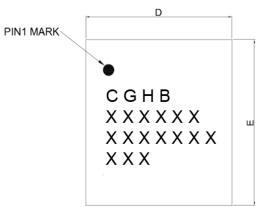

### 9 Package information

| Orderable<br>Device | Package<br>Type | Op Temp (°C) | Eco Plan    | Package<br>Marking               | Packing Option                 |

|---------------------|-----------------|--------------|-------------|----------------------------------|--------------------------------|

| CGHB2202            | 2 WLCSP         | -40 to 125   | RoHS & PAHs | CGHB<br>XXXXXX<br>XXXXXXX<br>XXX | Tape and Reel,<br>3000pcs/reel |

RoHS: PowerX defines "RoHS" to mean semiconductor products that are compliant with the current EU RoHS requirements for all 10 RoHS substances.

PAHs: PowerX defines "PAHs" to mean semiconductor products that are compliant with the current EU PAHs requirements for 18 PAHs substances.

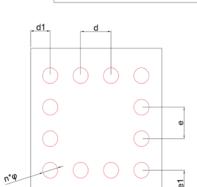

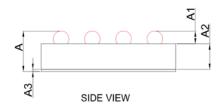

# COMMON DIMENSIONS (UNITS OF MEASURE=MILLIMETER)

| SYMBOL | ITEM                                      | MIN   | NOM   | MAX   |  |  |

|--------|-------------------------------------------|-------|-------|-------|--|--|

| Α      | PACKAGE HEIGHT                            | 0.460 | 0.501 | 0.542 |  |  |

| A1     | BALL HEIGHT                               | 0.137 | 0.161 | 0.185 |  |  |

| A2     | WAFER THICKNESS                           | 0.302 | 0.315 | 0.329 |  |  |

| А3     | BACKSIDE FILM<br>THICKNESS                | 0.022 | 0.025 | 0.028 |  |  |

| Ф      | BALL DIAMETER                             | 0.180 | 0.200 | 0.220 |  |  |

| D      | PACKAGE SIZE X                            | 1.705 | 1.725 | 1.745 |  |  |

| Е      | PACKAGE SIZE Y                            | 1.875 | 1.895 | 1.915 |  |  |

| d      | MIN BALL PITCH X                          |       | 0.400 |       |  |  |

| d1     | MIN BALL CENTER TO<br>PACKAGE SIZE X AXIS | 0.257 |       |       |  |  |

| е      | MIN BALL PITCH Y                          |       | 0.400 |       |  |  |

| e1     | MIN BALL CENTER TO<br>PACKAGE SIZE Y AXIS | 0.347 |       |       |  |  |

| n      | BALL COUNT                                |       | 12    |       |  |  |

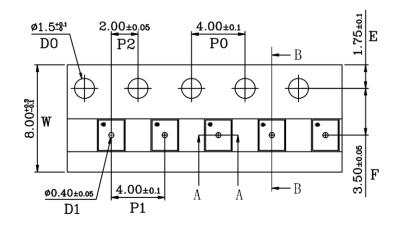

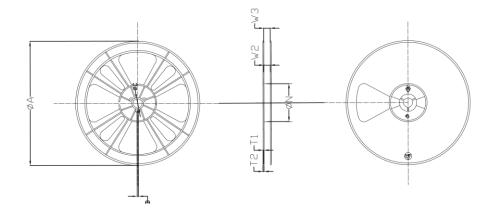

# 10 Tape and reel information

|      | Type/Size            |           |            |          | (UNI       | T:mm)    |           |        |        |

|------|----------------------|-----------|------------|----------|------------|----------|-----------|--------|--------|

| Type | W                    | P1        | Е          | F        | D0         | D1       | P0        | P2     | 10P0   |

| Size | $8.00^{+0.3}_{-0.1}$ | 4.00±0.10 | 1.75±0.10  | 3.5±0.05 | 1.50 +0.10 | 0.4±0.05 | 4.0 ±0.1  | 2±0.05 | 40±0.2 |

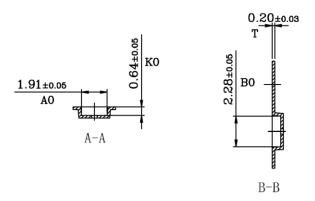

| Туре | A0                   | A1        | В0         | B1       | K0         | K1       | T         |        |        |

| Size | 1.91 ±0.05           |           | 2.28 ±0.05 |          | 0.64±0.05  |          | 0.20±0.03 |        |        |

| Item | Value&Tolerance |

|------|-----------------|

| Α    | 179±1.0         |

| В    | 2.0±0.2         |

| С    | 13.5±0.2        |

| N    | 54.8±0.2        |

| W2   | 9.0±0.2         |

| W3   | 9.2+1.0         |

| T1   | 1.2±0.2         |

| T2   | 1.5±0.2         |

# 11 Revision history

Major changes since the last revision

| Revision | Date     | Description of changes |

|----------|----------|------------------------|

| 0.8      | 2025-6-5 | 0.8 version release    |